# Area And Power Efficient Router In 2D Mesh NoC

[1] K.Swathi , [2]Dr.P.A.Harshavardhini [1] Vignan Institute Of Technology & Science , [2] Vignan Institute Of Technology & Science, [1] VLSI System Design (M.Tech), [2] Professor, Department of ECE

#### **ABSTRACT**

*Network-on-chip* (NoC) is another worldview in complex framework on-chip (SoC) plans that give productive on chip correspondence systems. It permits versatile correspondence and permits decoupling of and calculation. correspondence information is directed through the systems as far as bundles. The directing of information is for the most part done by switches. So the design of switch must be a productive one with a lower dormancy and higher throughput. In this undertaking we outlined, actualized and broke down three diverse switch structures for a system on chip correspondence. The switches have five ports, four ports associated with different ports in four distinct ways and the fifth port associated with the preparing component through a system interface. The principal design is a fundamental switch with demultiplexer and scheduler. The second design comprises of crossbar switch and referee. The third design utilizes the CDMA innovation that is famous in remote correspondence. The three structures were investigated for their execution as far as deferral, throughput and idleness and we presumed that CDMA switch performs superior to the next two.

#### 1. INTRODUCTION:

According to Moore's law the thickness of chip duplicates at regular intervals, so the parameters of a solitary chip get influenced of increment because of handling components on a chip. NOC is a parcel exchanged on-chip information exchange arrange that explains challenges looked by SOC of transport based correspondence. The essential elements of NOC are topology which characterizes the correspondence design, directing procedure which chooses how the information is steered from sender to recipient, switches and exchanging system which decides when the information course through the switches. NOC utilized just point to point wires for all system sizes and it builds the usage of wires.

90% of ASIC re-turns are because of Functional bugs. As the practical check chooses the nature of the silicon, we burn through 60% of the outline process duration just for the confirmation/recreation. To maintain a strategic distance from the postponement and meet the TTM, we utilize the most recent check strategies and advancements and quicken the confirmation procedure. This task encourages one to comprehend the total utilitarian check procedure of complex ASICs and SOC's and it offers chance to attempt the most recent confirmation techniques, programming ideas

like Object Oriented Programming of Hardware Verification Languages and advanced EDA devices, for the great confirmation.

To handle these issues, we present a zone and power effective switch in 2d work switch named NOC to accelerate the piece computational parts of profound learning calculations. Specifically, we use the tile methods, FIFO cushions, and pipelines to limit memory exchange tasks, and reuse the processing units to execute the huge size neural systems

The execution of the code is finished by verilog dialect. In usage picture input module planned in first stage, the picture module is composed with counter after that a FSM control module outlined in this the states are alter by key qualities. For each key esteem we have diverse states are relegated by the key qualities the states are changed.

By utilizing a few changes security is accommodated DSP circuits. The confusion is finished in FPGA innovation so the territory of chip and power dissemination is diminished. The frustrated DSP circuits are used in transmission, video pressure, wired and remote correspondence, bio restorative flag process and discourse process.

The archive of these is sorted out into seven sections. The part one is the Introduction, section two is the Literature Review, part three is the Block Diagram and Description of each square, section four is the product devices utilized for usage and dialect utilized for coding, section five is focal points and inconveniences of jumbling, 6th part is the outcome examination and

comparing yield waveforms of each square, seventh part is future extension and end.

### 2. RESEARCH WORK:

Multi-Processor Systems-on-Chip (MPSoCs) have been a reasonable new pattern in processor-based frameworks plan. Universally useful MPSoC creators have swung to the Network-on-Chip (NoC) interconnect model to outperform the constraints forced by customary transport or crossbar-based interconnection. This innovation is additionally a promising answer for wellbeing basic ventures where, basically because of intensity and weight limitations, there is an expanding need in frameworks for installed actualizing numerous functionalities upon a solitary shared processing stage.

This displays rough a correspondence method went for enhancing the vitality effectiveness of Network-on-Chip (NoC) based designs. The essential thought is a particular change, at run-time, of the voltage swing of the connections of the NoC to acquire an exchange off between the correspondence vitality utilization and the exactness of the running application. The proposed system is connected to a contextual investigation, to be specific, a JPEG encoder bringing about a vitality setting aside to 70% with a unimportant effect on the nature of the compacted picture.

The pattern in the semiconductor business is to introduce all the more exceedingly thick and useful MPSoC because of the expanding interest for interconnected gadgets (e.g., Internet of

Things). In this unique situation, these gadgets are holding an expanding measure of individual information from its clients. With the objective of ensuring clients against assaults, this proposes a protected engineering and gives the expenses of expanding the security for Networks-on-Chip (NoCs). The engineering is made out of a firewall fit for separating approaching and active system movement and encoding delicate data performing end-to-end security utilizing an AES figure square. The Firewall in addition to the AES builds the switch region by 193.7% and inactivity increments in the most dire outcome imaginable 395.92%. Regardless of this execution punishment, the activity is ensured against assaults. Considering that the infusion rate of uses is little (ordinarily 5-10%), a little execution overhead at the application level is normal.

With the expansion in the quantity of centers inserted on a chip the principle challenge for Multiprocessor System-on-Chip (MPSoC) stages is the interconnection between that enormous number of centers. Systems on-Chip (NoC) was acquainted with settle that test, by giving a versatile and particular answer for correspondence between the centers. In this, we present a configurable MPSoC structure considered RVNoC that creates synthesizable RTL that can be utilized in both ASIC and FPGA usage.

The proposed structure depends on the open source RISC-V Instruction Set Architecture (ISA) and an open source configurable dance based switch for interconnection between centers, with a center system interface of our outline to associate each center with its assigned switch. A benchmarking situation is created to assess variation parameters of the produced MPSoC. Combination of a solitary building square containing a solitary center with no peripherals, a switch, and a center system interface, utilizing 45nm innovation, demonstrates a region of 102.34 kilo Gate Equivalents (KGE), a greatest recurrence of 250 MHz, and a 9.9 µW/MHz control utilization

Expanding intricacy of outline and requirement for detachment the processing and correspondence zones in chips has coordinated the chip plan methods toward Network-On-Chip frameworks. NOC configuration depends on connecting precomposed centers and segments in a System-on-Chip Environment. The principle design is giving a successful foundation to speaking with wanted assets. The multifaceted nature and the extent of the systems in NOC increment correspondence cost among parts and plausibility of capricious disappointments in segments and correspondence circuits. Consequently proposing issue tolerant calculations is important in creating NOC design that is the inspiration of this examination work. This paper tends to restrictions of current directing calculations in adaptation to internal failure. The proposed calculation enhances adaptation to non-critical failure, diminishes the deferral in steering, and expands the unwavering quality of NOC frameworks utilizing fluffy directing. The trial results demonstrate a huge change in adaptation to internal failure

and unwavering quality with immaterial equipment overhead.

### 3. IMPLEMENTATION

## 3.1 Proposed Model

Systems on-Chip (NoCs) there is no "one size fits all" NoC engineering, as various silicon frameworks have altogether different necessities from their NoCs. For instance, in a System-on-Chip (SoC), the system utilization designs are known a monastery. Subsequently, the NoC can be integrated with precisely the correct connection capacities with respect to the required utilization. supporting Conversely, in a Field Programmable Gate Array (FPGA), the correspondence design is resolved when the chip is arranged to actualize some particular usefulness, and subsequently its physical format must give the adaptability to help an assortment of movement designs. In this paper, we center around NoC outline for FPGAs. A distinctive element of FPGA frameworks is that they incorporate a mix of hard and delicate functionalities.

The hard usefulness is actualized in silicon; it ordinarily incorporates unique reason modules like processors, multipliers, outside system and memory interfaces, and so forth. The delicate usefulness is arranged utilizing programmable components (door exhibits, flip-flops, and so forth.). Present day FPGAs contain a huge number of programmable components, notwithstanding extraordinary reason modules. As innovation scales, the sheer number of rationale units will render a level FPGA chip outline unmanageable.

This manner imagine a future FPGA that is composed progressively; whereby the chip is partitioned into abnormal state locales interconnected by a NoC. While architecting a FPGA NoC, one needs to choose which functionalities to actualize as hard centers and which to leave delicate. There is a tradeoff between the adaptability offered by delicate plans and the better execution offered by hard ones. Since between module correspondence is regularly a bottleneck, it is vital to outline the NoC design for superior. We along these lines advocate spreading out the framework, including metal wires and hardcoded switches in silicon. In the meantime. with a specific end goal to consider most extreme adaptability, the NoC framework ought to have the capacity to oblige various steering plans and a vast assortment of activity designs. To this end, we permit organize interfaces to be delicate. That is, every module has a configurable system interface (CNI) Simplistic directing plans, similar to XY, can utilize little interfaces, though more detailed source-steering plans may have the interfaces store substantial steering tables.

### 3.2 System Architecture:

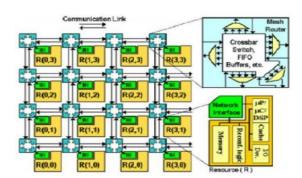

Fig 1: Noc architecture

A run of the mill NoC chip is a lattice of asset openings containing incorporated installed processors frameworks associated with one another by means of a multi-dimensional work/tree organize. In this manner, an ordinary NoC framework incorporates asset hubs, switch hubs, connections and system interface unit, and directing calculations for meet the prerequisites of the distinctive models. The switch hubs incorporate the directing controller and a referee for settling nearby course clashes.

The directing calculation as of now under thought can be named pseudodynamic since it's permitted just for limited powerful steering if there should arise an occurrence of switch clashes. Likewise, switch engineering ought to be balanced with various steering calculations. These affecting components possibly increment vulnerability condition for framework exhibitions, particularly organize dormancy, blockage, cost and different confinements. Since the switches don't precisely know resulting switches working conditions continuously.

So nearby execution advancement dependably exacerbates the entire framework execution. Utilizing these designs for to a great degree vast frameworks is extremely troublesome. We trust that NoC switch design ought to be straightforward, low-idleness, ease, and the quantity of information cradles ought to be insignificant later on.

As per the perspective of NoC as an examination field of SoC. We center around

developing doable, low-inertness and minimal effort correspondence driven plan.

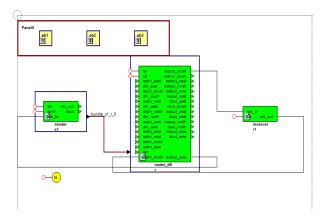

Fig 2: Noc Application Block Diagram

#### 4. RESULTS:

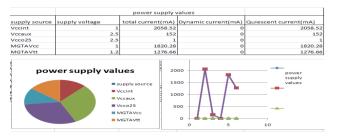

## 4.1 Power Analysis values:

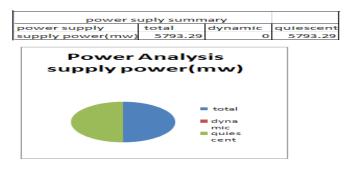

# 4.2 Power Supply Summary:

### 4.3 On-chip Power:

#### **4.4 Simulation Results:**

Recreation is utilized for testing, and their everything utilitarian projects, practical arrangements, timing compels, and details one needs to check there whether every one of the capacities are completed of course and redressed by reproductions.

In this recreation procedure at first considers inputs clock is 1 with 14us day and age then the ack is 1, reset 1 then the ack-down to 1 the principle check dout is 10. At that point the program gets the outcome as appeared above figure.

Change the estimations of yield the info clock is 1 with 14us day and age then the ack is 0 it reset the qualities and change reset as 0 then the yield of ack-down to 0, and the primary check dout is 00. At that point the program gets the outcome as appeared above figure.

### 5. CONCLUSION

In this venture, we have checked the usefulness of the NOC with the switch displaying in view of VERILOG where

cover focuses and distinctive experiments (like obliged, weighted and coordinated experiments) were confirmed. By utilizing these experiments we had enhanced the plan test parameters such region and intensity of the ROUTER and Network on the chip. In this venture, we have utilized one ace and four slaves to screen the ROUTER. Consequently the usefulness and testability of the ROUTER were moved forward.

### 6. REFERENCES

- 1. Dally, W.J., Towles, B.: Route Packets, Not Wires: On-Chip Interconnection Networks. In: Design Automation Conf., USA, pp. 683–689

- 2. Jantsch, A., Tenhunen, H.: Networks on Chip, pp. 3–39. Kluwer Academic Publishers, Hingham

- 3. Pande, P.P., Grecu, C., Ivanov0, A., Saleh, R.: Design of a Switch for Network on Chip applications. In: ISCAS, Bangkok, Thailand, vol. 5, pp. v217-v220

- 4. Kumar, S., Jantsch, A., Soininen, J.-P., Forsell, M., Millberg, M., Tiensyrja, K.: A network on chip architecture and design methodology. In: Proceedings of IEEE Computer Society Annual Symposium on VLSI, Pittsburgh, USA, pp. 105–112